Verilog Code Generator

Generate verilog code (.v file) of inaccurate adder or inaccurate multiplier based on user chosen options

As of 13 Jul 2021 (GMT+8), you will need to modify a tiny portion of generated verilog code. Click here to find out more. This edit in only required for ASIC based designs only. We are working to fix it

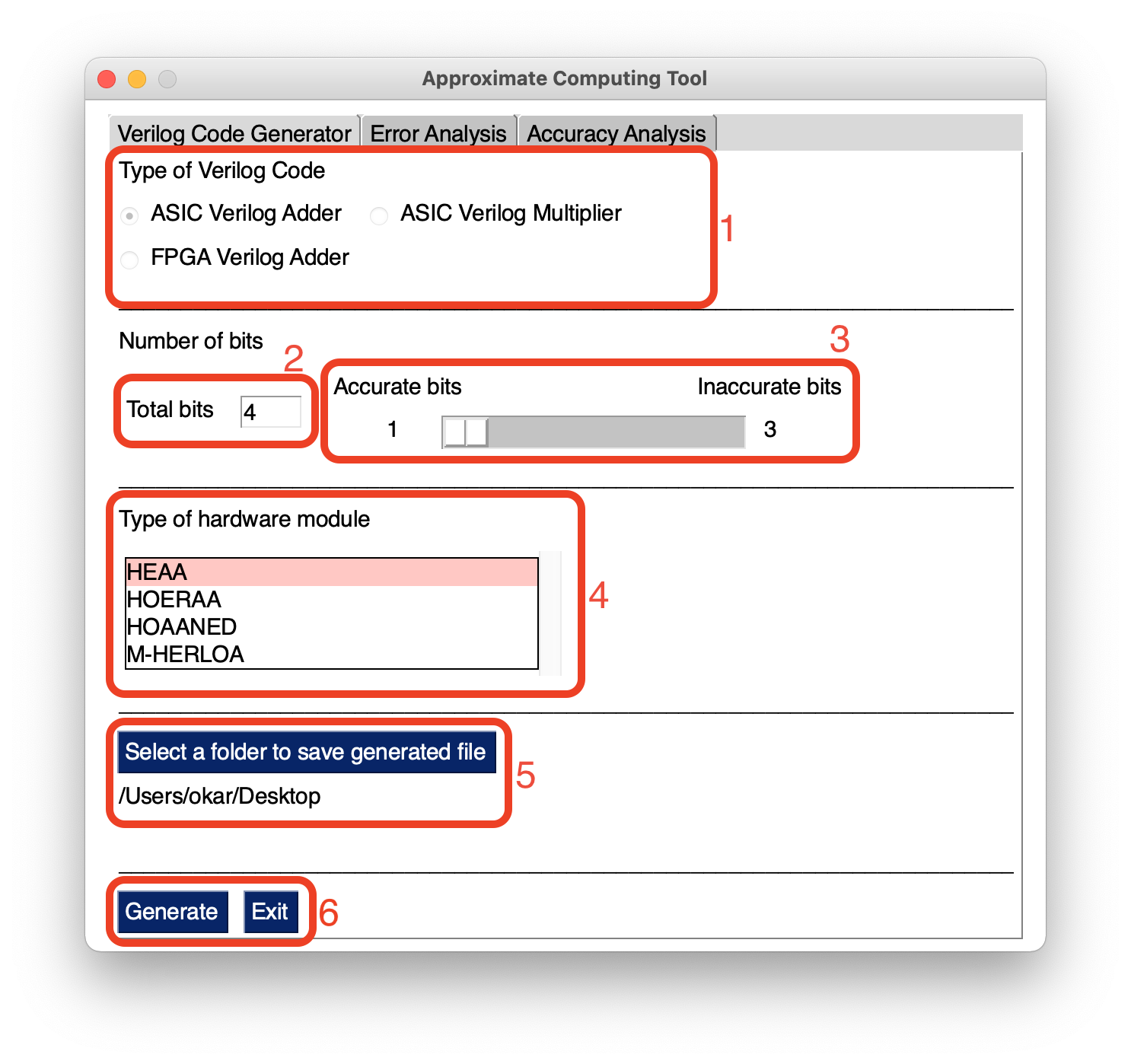

Adder Verilog Code Generator

Only integer inputs are accepted. Will prompt an error if the input are not valid integer

-

Type of Verilog Code to generate, choose one of

[ASIC Verilog Adder, ASIC Verilog Multiplier, FPGA Verilog Adder]- Default Options:

ASIC Verilog Adder

- Default Options:

-

Total number of bits for the module verilog code generation

- Default Options:

4

- Constraints:

4 <= total_bits <= 32

- Default Options:

-

Accurate bits and Inaccurate bits selection. Move slider to adjust

- Default Options:

acc_bits = 1inacc_bits = 3

- Constraints:

3 <= inacc_bits <= total_bits - 1

- Default Options:

-

Type of hardware module to generate, chose one of

[HEAA, HOERAA, HOAANED, M-HERLOA]- Default Options:

HEAA

- Default Options:

-

Choose location in computer to save generated verilog file

- Default Options:

Desktop

- Default Options:

-

Generate verilog code or exit

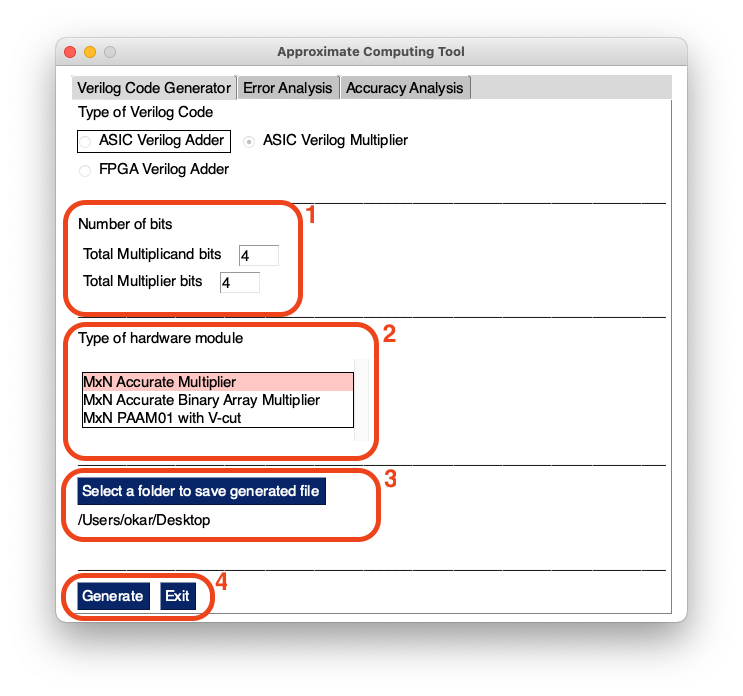

Multiplier Verilog Code Generator (ASIC Verilog Multiplier)

Only integer inputs are accepted. Will prompt an error if the input are not valid integer

-

Multiplicand bits and Multiplier bits

- Default Options:

4

- Constraints:

multiplicand_bits >= 3multiplier_bits >=3

- Default Options:

-

V-cut (only for MxN AAM01 with V-cut)

- Default Options

3

- Constraints:

0 <= v_cut <= multiplicand_bits + multiplier_bits - 3

- Default Options

-

Type of hardware module to generate, chose one of

[MxN Accurate Multiplier, MxN Accurate Binary Array Multiplier, MxN AAM01 with V-cut]- Default Options:

MxN Accurate Multiplier

- Default Options:

-

Choose location in computer to save generated verilog file

- Default Options:

Desktop

- Default Options:

-

Generate verilog code or exit

As of 13 Jul 2021 (GMT+8), you will need to modify a tiny portion of generated verilog code. Click here to find out more. This edit in only required for ASIC based designs only. We are working to fix it